Half and Full Adders

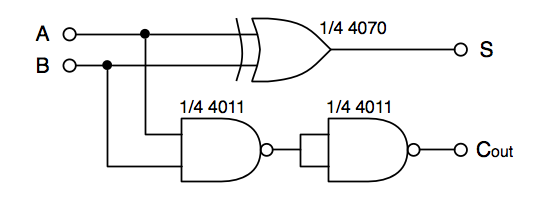

The following is a classic half adder circuit, built with XOR and NAND gates:

The XOR gate decides the parity of the output bit S, and the two NAND gates act as an AND gate for the inputs, deciding whether the carry bit should be set.

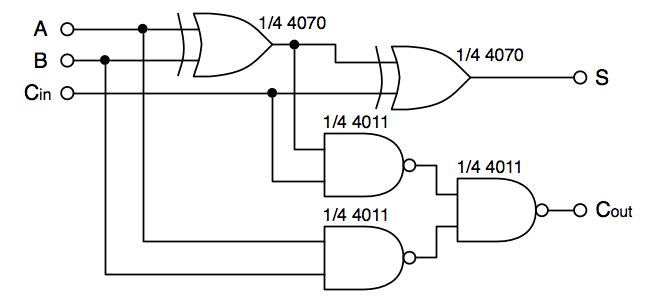

Here’s a full adder, which also deals with an incoming carry bit:

The Wikipedia article discusses a number of possibilities for deciding on the carry bit. This one has the virtue of using only NAND gates.